Implementacja sprzętowa protokołu PS/2 w układzie FPGA XILINX Spartan III XC3S1000

Układy FPGA (Field Programmable Gate Array) mają coraz większą rzeszę zwolenników, również wśród pasjonatów i amatorów techniki cyfrowej. Duża funkcjonalność, malejące ceny, darmowe zaawansowane środowiska programistyczne oraz rozbudowane języki opisu sprzętu skutkują coraz większym zainteresowaniem układami FPGA.

Wiele projektów realizowanych w strukturach programowalnych wymaga komunikacji z użytkownikiem przy pomocy przycisków. Zwykle taka potrzeba zachodzi w trakcie weryfikacji działania złożonego układu cyfrowego. Proces ten jest szczególnie ważnym etapem tworzenia oprogramowania i zazwyczaj podzielony jest na kilka części mających na celu zapewnienie, że produkt końcowy będzie wysokiej jakości. Każdy etap testowania polega na poddaniu badanego modułu odpowiednim wymuszeniom oraz obserwacji jego odpowiedzi. W tym celu stosuje się wygodne narzędzie umożliwiające komunikację układu ze światem zewnętrznym.

W dostępnych na rynku płytach prototypowych z układami FPGA montowane są przyciski typu microswitch. Ich liczba może być niewystarczająca dla potrzeb projektanta. Ze względu na występowanie drgań zestyków przycisku mechanicznego zachodzi konieczność projektowania dodatkowych układów wewnątrz struktury FPGA. Z drugiej strony niemal każda płyta prototypowa wyposażona jest w interfejs umożliwiający podłączenie do niej standardowej klawiatury komputerowej PS/2. Warto wykorzystać to podczas planowania komunikacji użytkownika z zaprojektowanym układem. Koszt gotowej klawiatury komputerowej jest tak niski, że nie ma sensu projektować jej od początku, lepiej skorzystać z gotowego rozwiązania dostępnego w wielu konfiguracjach i wykonaniach.

Przedstawiony moduł w strukturze FPGA może być wykorzystany do projektów większych układów sterowania lub kontroli, gdzie pełna klawiatura będzie zastosowana do wprowadzania danych przez użytkownika.

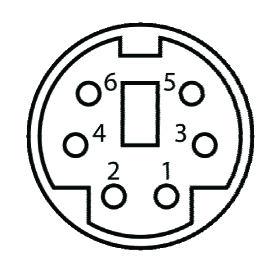

Złącze oraz interfejs klawiatury PC (PS/2)

Złącze PS/2 ma sześć pinów (rys. 1), z czego tylko cztery wykorzystane są w interfejsie klawiatury PC. Klawiatura zasilana jest napięciem +5 V. Sygnał danych oraz sygnał zegarowy transmitowane są kolejno poprzez piny 1 oraz 5. Urządzenie zasilane jest z pinu 4. Masa urządzenia podłączona jest do pinu 3. Pozostałe wyjścia złącza (2 oraz 6) nie są używane przez standardową klawiaturę PC.

Protokół PS/2. Transmisja danych w protokole PS/2 odbywa się szeregowo, synchronicznie. Sygnał zegarowy nadawany jest wyłącznie przez urządzenie PS/2 [1].

Jeżeli następuje jakieś zdarzenie (np. wciśnięcie lub zwolnienie klawisza), urządzenie wysyła do hosta dane zgrupowane w 11-bitowej ramce (rys. 2). Każda ramka zawiera bit startu (zawsze równy 0), 8 bitów danych, bit parzystości (kontrola nieparzystości) oraz bit stopu (zawsze równy 1).

Transmisja danych, gdy host wysyła rozkaz do urządzenia, przebiega nieco inaczej (rys. 3). By rozpocząć transmisję danych, host ustawia sygnał zegarowy na poziom niski. Po 100 µs przywraca sygnał zegarowy na poziom wysoki oraz ustawia sygnał danych na poziom niski. Jest to informacja dla urządzenia, by zaczęło nadawać sygnał zegarowy. Przy każdym zboczu opadającym sygnału zegarowego host wystawia na wyjście DATA (pin 1) kolejny bit ramki. Po jedenastym zboczu narastającym sygnału zegarowego urządzenie wysyła bit ACK.

Kodowanie klawiszy standardowej klawiatury PC

Istnieją trzy sposoby kodowania klawiszy, z czego powszechnie używany jest kod nr 2 (obok kodu nr 1 oraz kodu nr 3). W kodzie tym, każdy klawisz ma dwie unikalne 8-bitowe wartości liczbowe:

- make code – wysyłany w chwili naciśnięcia klawisza

break code – wysyłany w chwili zwolnienia klawisza.Kody make oraz break wybranych klawiszy (kod nr 2) KEY MAKE BREAK A 1C F0, 1C 0 45 F0, 45 UP ARROW E0, 75 E0, F0, 75 KP 8 75 F0, 75

Klawisze w kodzie nr 2 można podzielić na dwie grupy. Pierwszą stanowią klawisze, których make code mieści się w jednej ramce. Druga grupa zawiera klawisze (tzw. rozszerzone), których make code wymaga wysłania dwóch ramek. Pierwsza ramka klawisza rozszerzonego zawiera zawsze wartość E0. Podczas zwalniania klawisza wysyłany jest break code, co najmniej dwuramkowy i zawiera zawsze ramkę F0.

Strukturalny schemat ideowy modułu

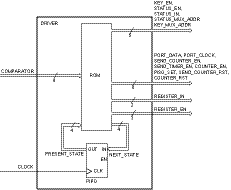

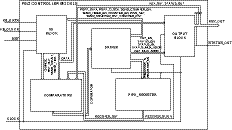

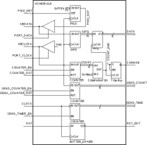

Moduł sterownika protokołu PS/2 (rys. 4) ma 4 wejścia: zegarowe, resetujące, sygnał KB_DATA, KB_CLOCK. Na wyjściu modułu jest 8-bitowy kod aktualnie wciśniętego klawisza oraz jednobitowy znacznik kodu rozszerzonego. Układ składa się z pięciu bloków funkcjonalnych: układu sterującego, modułu wejścia/wyjścia, modułu wyjścia, rejestru oraz zespołu komparatorów.

Układ sterujący (rys. 5) to typowa maszyna Moore’a zrealizowana w oparciu o rejestr PIPO oraz odpowiedni układ kombinacyjny. Rejestr PIPO przechowuje aktualny stan maszyny. Wartości sygnałów sterujących maszyny zależą wyłącznie od jej stanu aktualnego. Układ jest synchronizowany zewnętrznym sygnałem zegarowym o częstotliwości 1 MHz.

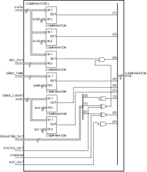

Moduł REGISTER (rys. 6) pełni funkcję 3-bitowego rejestru przechowującego informacje o aktualnie przychodzącym rozkazie. Zawiera pola określające, czy klawisz, którego kod aktualnie jest odbierany ma być usunięty (F0), jest rozszerzony (E0) oraz czy nastąpiła zmiana w rejestrze PIPO modułu I/O. Stany odpowiednich bitów rejestru zależą od aktualnego stanu rozkazu.

- REGISTER_OUT(0): 1 jeżeli przyszła ramka F0, 0 w przeciwnym wypadku

- REGISTER_OUT(1): 1 jeżeli przyszła ramka E0, 0 w przeciwnym wypadku

- REGISTER_OUT(2): zmienia swą wartość na przeciwną przy każdym przyjściu nowej ramki.

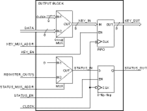

Moduł I/O (rys. 7) odpowiada za odbiór i nadawanie danych. Zawiera dwa bufory trójstanowe, które ustalają kierunek transmisji danych. Gdy dane są odbierane, na wyjściu buforów jest stan wysokiej impedancji. W pierwszej kolejności odbierane bity trafiają do rejestru SIPO. Gdy zostaną zliczone wszystkie zbocza zegarowe ramki, zawartość tego rejestru przerzucana jest do rejestru PIPO, dzięki czemu możliwy jest dalszy odbiór danych w rejestrze SIPO. Gdy dane mają być wysłane, na wyjście bufora danych przekazywany jest sygnał wyjściowy rejestru PISO. Wraz ze zboczem opadającym sygnału zegarowego, każdy kolejny bit przekazywany jest na wyjście układu. Moduł I/O zawiera też układy licznikowe używane podczas wysyłania danych z hosta. Blok BUTTON_DRIVER pełni rolę przerzutnika monostabilnego. Jego obecność wymagana jest ze względu na występowanie drgań zestyków przycisku mechanicznego RST.

Moduł COMPARATORS (rys. 8) kształtuje sygnał na wejście układu sterowania. Porównywane są odpowiednie sygnały z wartościami stałymi lub innymi sygnałami. Sprawdzane jest, czy wartość sygnału DATA zawiera rozkaz usunięcia (F0) lub kod rozszerzony (E0). Jeżeli aktualnie przetwarzany rozkaz sygnalizuje zwolnienie klawisza, określone zostaje, czy jego kod zgodny jest z kodem klawisza na wyjściu całego modułu (aktualnie wciśniętego). Komponent COMPARATORS nadzoruje zmiany w rejestrze PIPO modułu I/O oraz stan liczników służących do wysyłania danych.

Moduł wyjścia (rys. 9) zawiera dwa multipleksery (jeden grupowy) dwuwejściowe ustawiające sygnały na wejściu rejestru wyjściowego i przerzutnika typu D. Adresy multiplekserów i sygnały EN przerzutników ustalane są przez układ sterownia.

Podsumowanie

Zaprojektowany sterownik protokołu PS/2 zaimplentowano sprzętowo w układzie FPGA Xilinx Spartan III XC3S1000 [4]. Projekt zrealizowano w języku VHDL w środowisku programistycznym Xilinx ISE WebPack 8.2i [6]. Proces weryfikacji poprawności działania układu rozbity został na dwa etapy. W pierwszym przebadano zachowanie pojedynczych komponentów składowych, oraz całego układu w środowisku symulacyjnym (ModelSim XE III v.6.3.c [5] firmy Mentor Graphics). Drugi etap testowania polegał na sprawdzeniu działania układu w rzeczywistej strukturze FPGA. Wykorzystano w tym celu płytę uruchomieniową LiveDesign Evaluation Board firmy Altium [7], której „sercem” jest układ FPGA Spartan 3 XC3S1000 firmy Xilinx. Weryfikacja zakończyła się sukcesem, a sterownik PS/2 stosowany jest w złożonych projektach jako moduł pomocniczy do wprowadzania danych dla procesu testowania innych struktur logicznych.

Bibliografia

- Chapweske A.: The PS/2 Keyboard Interface, 2003.

- Skahill K.: Język VHDL. Projektowanie programowalnych układów logicznych. WNT, Warszawa 2004.

- Zwoliński M.: Projektowanie układów cyfrowych z wykorzystaniem języka VHDL. WKiŁ, Warszawa 2007.

- Xilinx.

- ModelSim Xilinx Edition III.

- ISE WebPACK Design Software.

- LiveDesign Evaluation Boards.

Szymon Kozień, dr inż. Wojciech Mysiński - Koło Naukowe Techniki Cyfrowej

Wydziale Inżynierii Elektrycznej i Komputerowej

Politechnika Krakowska