Sterownik urządzenia do pomiaru słabych sygnałów optycznych na bazie FPGA

FPGA (Field Programmable Gate Array) to rozbudowane, reprogramowalne macierze bramek logicznych, wyposażone zazwyczaj w szereg dodatkowych urządzeń sprzętowych, takich jak mnożarki czy przetworniki analogowo-cyfrowe.

FPGA pełnią coraz większą rolę w projektowaniu układów cyfrowych ASIC i mikroprocesorów. Ich atrakcyjność wynika z szybkości działania, olbrzymich zasobów logicznych i prostoty realizacji projektów. Nie tylko usprawniają one proces opracowywania nowych układów cyfrowych, ale coraz częściej stanowią podstawę układów sterowania gotowych urządzeń.

Proces projektowania układu sprowadza się do opisania jego struktury lub sposobu działania w wybranym języku opisu sprzętu. Ze względu na duże zasoby logiczne oraz wbudowane mnożarki sprzętowe, w wielu zastosowaniach z powodzeniem mogą one konkurować z mikroprocesorami. Ich dodatkową zaletą jest możliwość równoległego uruchamiania procesów poprzez tworzenie struktur współbieżnych.

Dzięki tej właściwości układy programowalne umożliwiają kontrolę wielu złożonych procesów w czasie rzeczywistym. Właściwość tę wykorzystuje się między innymi w telekomunikacji. Pojawiają się również przykłady stosowania układów programowalnych w takich dziedzinach, jak napęd elektryczny, robotyka i automatyka. W pracy pokazano przykład wykorzystania układu FPGA do budowy sterownika urządzenia do pomiaru słabych sygnałów optycznych (chopper).

Projekt prezentowanego sterownika zrealizowano w języku VHDL (Very High Speed Integrated Circuits Hardware Description Language) [2]. Do realizacji projektu wykorzystano środowisko Xilinx ISE Design Suite 10.1 WebPack [5]. Projekt zaimplementowano w module prototypowym Basys [3] z układem FPGA Spartan 3E 100 firmy Xilinx [5] (rys. 1).

Zasada działania urządzenia

Chopper stosuje się w celu ograniczenia wpływu szumów własnych czujników optycznych i wzmacniaczy w torze wzmocnienia na wyniki pomiarów słabych sygnałów optycznych. Zasada działania tego urządzenia polega na naprzemiennym wykonywaniu pomiarów sygnałów z zaciemnionego i oświetlonego czujnika, a następnie wyznaczeniu sygnału użytecznego, jako ich różnicy. Pomiary te wykonuje się w krótkich odstępach czasu tak, aby parametry pracy układu pomiędzy dwoma kolejnymi pomiarami nie zmieniały się w sposób istotny. Zakłada się przy tym, że wartość szumów własnych układu pomiędzy kolejnymi pomiarami nie ulega zmianie. Do praktycznej realizacji tego zadania najczęściej wykorzystuje się wirującą tarczę z otworami. Tarcza naprzemiennie zasłania lub odsłania czujnik pomiarowy, którym najczęściej jest fotodioda lub fotopowielacz [4].

Zadaniem projektowanego układu sterowania jest utrzymanie zadanej prędkości wirowania tarczy napędzanej silnikiem prądu stałego, synchronizacja pomiarów z chwilowym położeniem kątowym tarczy, odczyt, zapamiętanie i uśrednienie wyników pomiarów, wyznaczenie ich różnicy i prezentacja w formie wykresu na ekranie monitora VGA. Czynności te realizowane są w czasie rzeczywistym.

Do napędu tarczy przewidziano silnik prądu stałego sprzężony z enkoderem o rozdzielczości 1000 impulsów na obrót. Przy prędkości 10 000 obr./min. częstotliwość zliczanych impulsów z enkodera przekracza 16,5 kHz, a pomiary wykonywane są z częstotliwością dwa razy wyższą. Wyniki pomiarów przesyłane są następnie magistralą SPI do rejestrów zatrzaskowych, skąd pobierane są do dalszej części układu, przetwarzane i przesyłane do monitora VGA. Na ekranie monitora prezentowane są wyniki pomiaru uzyskane z oświetlonego i zaciemnionego czujnika oraz ich różnica. Przy częstotliwości odświeżania obrazu 50 Hz, rozdzielczości 640 × 480 pikseli i 256 kolorach, kolejne bajty danych muszą być wysyłane do monitora z częstotliwością ponad 15 MHz [1]. Przedstawione parametry świadczą o wysokich wymaganiach w stosunku do tego układu, którym nie jest w stanie sprostać znaczna część mikroprocesorów.

Analiza układu

W wyniku analizy funkcjonalnej układ podzielono na trzy główne bloki funkcjonalne:

- sterowania silnikiem prądu stałego

- pomiarowy (z zewnętrznym przetwornikiem ADC)

- obsługi monitora.

Każdy z tych bloków podzielono na prostsze moduły, które opisano w języku VHDL. Blok sterowania silnikiem prądu stałego składa się z dzielnika wstępnego, licznika impulsów zegarowych, licznika impulsów z enkodera i generatora PWM. Dzielnik wstępny zastosowano w celu obniżenia częstotliwości taktowania części układu do 5 MHz. Zastosowany moduł prototypowy taktowany jest sygnałem o częstotliwości 100 MHz. Sygnał 5 MHz podawany jest na wejście licznika odmierzającego interwały czasu o okresie 1 s, który co sekundę kasuje licznik impulsów z enkodera. Pomiar prędkości silnika odbywa się na zasadzie zliczania impulsów z enkodera. Stan licznika porównywany jest z wartością zadaną i na tej podstawie ustalany jest współczynnik wypełnienia sygnału PWM. Wypełnienie zmieniane jest co 1 s o 1 % do chwili osiągnięcia wartości zadanej. W związku z tym zadana prędkość silnika zostaje ustalona po czasie nie dłuższym niż 100 s. Podczas wykonywania pomiarów wartość współczynnika wypełnienia sygnału PWM pozostaje stała.

Blok odczytu i zapisu wyników pomiarów składa się z licznika impulsów z enkodera, licznika numeru pomiaru, modułu inicjalizacji pomiaru, interfejsu SPI, oraz dwóch rejestrów, do których zapisywane są wyniki. Licznik impulsów z enkodera służy do wyznaczania położenia tarczy w zakresie jednego pełnego obrotu. Sygnały z wyjścia tego licznika podawane są do modułu inicjalizacji pomiaru, który synchronizuje wykonywanie pomiarów z położeniem kątowym tarczy. Pomiary wykonywane są przy dwóch stanach licznika, odpowiadających odpowiednim pozycjom tarczy wirującej przy oświetlonym i zaciemnionym czujniku.

Odczyt wartości zmierzonych z przetwornika ADC odbywa się poprzez interfejs SPI. Blok ten adresuje odpowiednie rejestry, do których zapisywane są wyniki pomiarów sygnału lub tła. Urządzenie uśrednia wyniki 32 pomiarów.

Blok wyjściowy służy do wyświetlania wyników pomiarów na ekranie monitora VGA. Składa się on z modułu wyznaczającego różnicę zmierzonych sygnałów, modułu synchronizacji i generatora obrazu. Moduł generatora obrazu służy do wyświetlania danych pobieranych z rejestrów oraz z modułu wyznaczającego ich różnicę.

W trakcie realizacji poszczególnych modułów funkcjonalnych przeprowadzona została symulacja ich działania. Na podstawie uzyskanych przebiegów czasowych stwierdzono poprawność ich działania.

Synteza układu

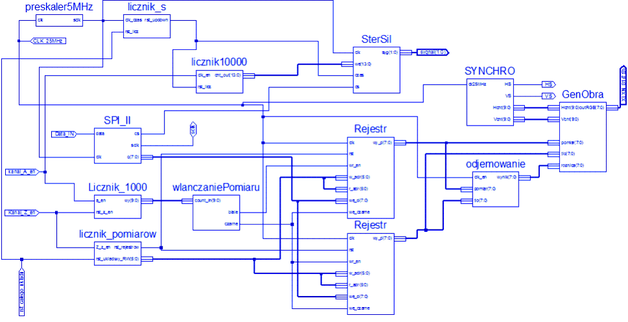

Po opracowaniu elementów składowych wykonano syntezę układu. Wyjścia rejestrów zawierających uśrednione wyniki pomiarów połączone zostały z modułem służącym do obliczania sygnału użytecznego oraz modułem przeznaczonym do prezentacji wyników na monitorze. Syntezę układu wykonano w module graficznym. Kompletny schemat zaprojektowanego układu pokazano na rys. 2. Po dokonaniu syntezy projekt zaimplementowano w układzie prototypowym (rys. 3) i sprawdzono poprawność jego działania.

Podsumowanie

Celem projektu było opracowanie kompletnego sterownika urządzenia do pomiaru słabych sygnałów optycznych i jego implementacja w układzie FPGA. Podczas realizacji projektu wykorzystano elementy wcześniej opracowanej (przy współudziale autora) biblioteki VHDL. Jedynie w przypadku modułu synchronizacji w bloku obsługi monitora VGA bazowano na elemencie biblioteki udostępnionej na stronie internetowej firmy Digilent [3], który dostosowano we własnym zakresie do potrzeb projektu. Wszystkie pozostałe elementy biblioteki opracowano w ramach prac koła lub pracy dyplomowej.

Uzyskany rezultat świadczy o tym, że układ programowalny z powodzeniem realizuje założony cel i może zastąpić w tym zastosowaniu dobrej klasy procesor.

Projekt po zaimplementowaniu zajął 68 % zasobów układu Spartan 3E 100, najmniejszego z tej rodziny. Pozostała wolna struktura umożliwia dalszą rozbudowę układu i zwiększenie jego funkcjonalności, na przykład poprzez dodanie interfejsu komunikacyjnego do przesyłania wyników pomiarów do komputera lub do ich zapisu na kartę SD. Dzięki współbieżności zaimplementowanych modułów rozbudowa układu nie powinna wpłynąć na szybkość jego działania.

Bibliografia

- Grzesik S.: Sterownik urządzenia do pomiarów małych sygnałów optycznych na bazie układu FPGA, Praca dyplomowa, Politechnika Opolska 2009.

- Majewski J., Zbysiński P.: Układy FPGA w przykładach. Wydawnictwo BTC, Warszawa 2007.

- Digilent Inc. - Digital Design Engineer's Source

- Rotating Disc Optical Choppers

- Xilinx Inc.

Sebastian Grzesik, dr inż. Krzysztof Tomczewski – SKN Spektrum, Politechnika Opolska

![Rys. 1. Moduł prototypowy Basys firmy Digilent z układem FPGA Spartan 3E 100 [3] Rys. 1. Moduł prototypowy Basys firmy Digilent z układem FPGA Spartan 3E 100 [3]](/var/aol/storage/images/par/forum-mlodych/studenckie-kolo-naukowe-spektrum/sterownik-urzadzenia-do-pomiaru-slabych-sygnalow-optycznych-na-bazie-fpga/57322-2-pol-PL/Sterownik-urzadzenia-do-pomiaru-slabych-sygnalow-optycznych-na-bazie-FPGA_articleimage.png)

![Rys. 1. Moduł prototypowy Basys firmy Digilent z układem FPGA Spartan 3E 100 [3] Rys. 1. Moduł prototypowy Basys firmy Digilent z układem FPGA Spartan 3E 100 [3]](/var/aol/storage/images/media/par/7-8_10/forum/grzesik-300e.png/75298-1-pol-PL/grzesik-300e.png_medium.png)